By

#### Ahmet Alper Goksoy

A preliminary report for the degree of

#### Doctor of Philosophy

(Department of Electrical and Computer Engineering)

#### at the

#### UNIVERSITY OF WISCONSIN-MADISON

2023

Preliminary Examination Date: 06/01/2023

Preliminary Exam Committee:

Umit Y. Ogras, Associate Professor, Electrical and Computer Engineering, University of Wisconsin-Madison

Yu Hen Hu, Professor, Electrical and Computer Engineering, University of Wisconsin-Madison

Younghyun Kim, Assistant Professor, Computer Sciences, University of Wisconsin-Madison

Chaitali Chakrabarti, Professor, Electrical, Computer and Energy Engineering, Arizona State University

Dedicated to my son, my parents Ayşe Gülnihal and Ismail Hakkı, my brother Osman Gökalp, and my wife Betül.

#### CONTENTS

Contents ii

List of Tables iv

List of Figures v

Abstract viii

- **1** Introduction 1

- **2** Literature Review 10

- 2.1 Chiplet-based Architectures 10

- 2.2 Home-based Rehabilitation Systems 12

- 2.3 Task Scheduling Techniques for Heterogeneous Architectures 14

- 3 Big-Little Chiplets for In-Memory Acceleration of DNNs: A Scalable Heterogeneous Architecture 17

- 3.1 Overall Architecture 17

- 3.2 Parameters of the Big-Little Architecture and Mapping 20

- 3.3 Experimental Evaluation 26

- 4 Energy-Efficient On-Chip Training for Customized Home-based Rehabilitation Systems 38

- 4.1 Home-Based Rehabilitation System 38

- 4.2 Experimental Results 43

- 5 Proposed Work 1: Communication-Aware Sparse Neural Network Optimization 52

- 6 Proposed Work 2: Carbon Footprint Optimization 56

- 7 Other Work: DAS: Dynamic Adaptive Scheduling for Energy-Efficient Heterogeneous SoCs 60

- 7.1 Dynamic Adaptive Scheduling Framework 60

- 7.2 Experimental Evaluations 65

- 8 Conclusions and Future Directions 71

Bibliography 74

## LIST OF TABLES

| 3.1 | Set of configurations considered to determine big-little chiplet and NoP       | -  |

|-----|--------------------------------------------------------------------------------|----|

| 2.2 | structure                                                                      | 27 |

| 3.2 | Performance comparison of each component of a homogeneous (Little              |    |

|     | only, Big only) chiplet architecture and the heterogeneous Big-Little          | 20 |

| 2.2 | IMC chiplet architecture for VGG-19 on CIFAR-100                               | 28 |

| 3.3 | Performance comparison of a homogeneous (Little only, Big only) chiplet        |    |

|     | architecture and the heterogeneous Big-Little IMC chiplet architecture         |    |

|     | for different DNNs                                                             | 30 |

| 3.4 | Ratio between DRAM energy and compute energy for VGG-16 and VGG-               |    |

|     | 19 with systems having different number of chiplets (**All weights of          |    |

|     | VGG-19 fit on chip with this configuration, significantly reducing the         |    |

|     | DRAM energy)                                                                   | 34 |

| 3.5 | Comparison with other platforms for ResNet-50 on ImageNet (*reported           |    |

|     | in [1])                                                                        | 34 |

| 4.1 | Random set configurations for experimental evaluations and training            |    |

|     | results of the baseline <i>mmWave-CNN</i> model                                | 44 |

| 4.2 | Hardware results for <i>mmWave-CNN</i> model inference and training on         |    |

|     | Jetson Xavier NX with 2 configurations and our framework with 2 con-           |    |

|     | figurations and the speedup comparisons. $128 \times 128$ and $256 \times 256$ |    |

|     | represent the crossbar array sizes. (P: PHR, J: Jetson)                        | 47 |

| 4.3 | Hardware results for <i>RGB-CNN</i> inference on Jetson Xavier NX with 6       |    |

|     | CPU cores and our framework with 256 $\times$ 256 crossbars                    | 50 |

| 7.1 | Type of performance counters used by DAS framework                             | 60 |

| 7.2 | Classification accuracies and storage overhead of DAS models with              |    |

|     | different machine learning classifiers and features                            | 68 |

## LIST OF FIGURES

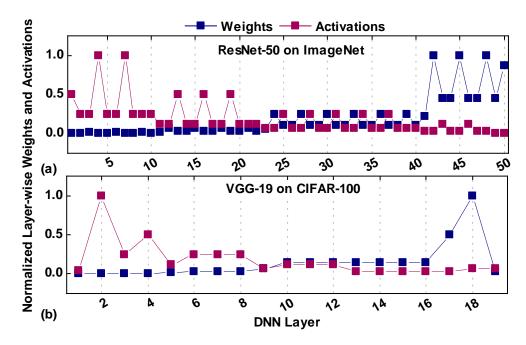

| 1.1 | Normalized layer-wise activation/weight distribution for (a) ResNet-50 (ImageNet) and (b) VGG-19 (CIFAR-100). Initial/latter layers are activation/weight dominated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

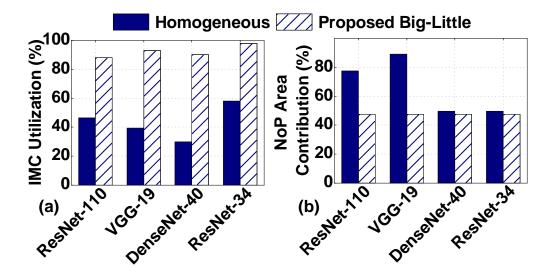

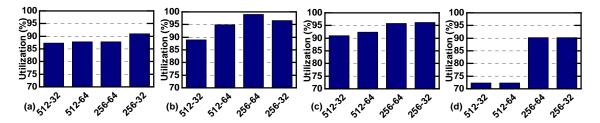

| 1.2 | IMC utilization for different DNNs using a homogeneous chiplet RRAM IMC architecture [2] and the proposed heterogeneous big-little chiplet architecture. The heterogeneous big-little architecture improves the IMC utilization.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4  |

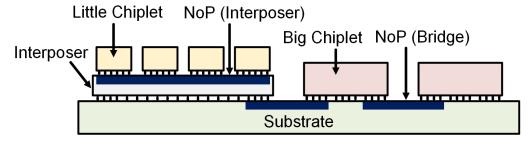

| 2.1 | Cross-sectional view of the big-little chiplet-based IMC architecture. The architecture consists of a little chiplet bank with little chiplets ( connected by an NoP within the interposer and a big chiplet bank with big chiplets connected by a bridge NoP. NoP properties: 1.5–8mm length, $2$ – $4.5\mu m$ pitch, and $0.5$ – $2\mu m$ width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11 |

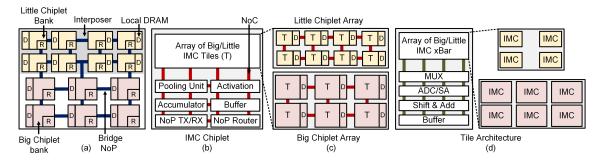

| 3.1 | (a) Overview of the big-little chiplet IMC architecture. The little chiplet bank utilizes smaller chiplets connected by a interposer-based NoP while the big chiplet bank utilizes bigger chiplets connected by a bridge-based NoP. Each chiplet utilizes a local DRAM, (b) IMC chiplet architecture (big and little). Each chiplet consists of an array of IMC tiles and a dedicated NoP transceiver and router, (c) The little chiplet bank consists of fewer and smaller tiles while the big chiplet bank consists of more bigger tiles. Both chiplet structures utilize a mesh-based NoC for on-chip communication, and (d) Structure of each tile within the big and little chiplet. It consists of an array of IMC crossbar arrays and associated peripheral circuits with an interconnect similar to that in [3]. The little chiplet consists of fewer and smaller IMC crossbars while the big chiplet |    |

|     | has larger and more IMC crossbar arrays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18 |

| 3.2 | IMC utilizations for different DNNs across different big-little chiplet-                      |    |

|-----|-----------------------------------------------------------------------------------------------|----|

|     | based RRAM IMC configurations for (a) ResNet-110, (b) ResNet-34, (c)                          |    |

|     | VGG-19, (d) DenseNet-40. Based on the utilization, we choose crossbar                         |    |

|     | size of big chiplet as $256 \times 256$ and crossbar size of little chiplet as $64 \times 64$ |    |

|     | (256–64)                                                                                      | 28 |

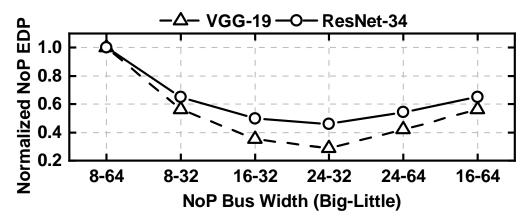

| 3.3 | Normalized NoP EDP for different bus-widths for VGG-19 and ResNet-                            |    |

|     | 34. The NoP with bus width of 24 for big and 32 for little chiplets (24–32)                   |    |

|     | shows lowest EDP                                                                              | 30 |

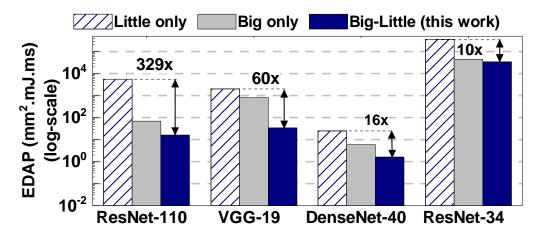

| 3.4 | EDAP comparison (log-scale) of the big-little chiplet-based RRAM IMC                          |    |

|     | architecture to 'Little only' and 'Big only' chiplet-based RRAM IMC ar-                       |    |

|     | chitectures. The big-little architecture achieves up to $329 \times$ improvement              |    |

|     | compared to 'Little only' architecture                                                        | 33 |

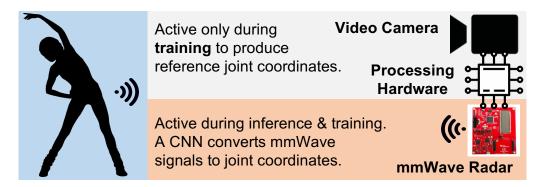

| 4.1 | Illustration of the target rehabilitation system. The RGB camera is used                      |    |

|     | only during training to generate the reference joint coordinates when the                     |    |

|     | initial model is customized to the target user. Once the model that uses                      |    |

|     | mmWave signals is trained, only the mmWave radar is used for inference.                       | 39 |

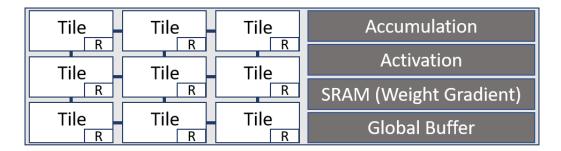

| 4.2 | The architecture of IMC-based hardware accelerator. Feedforward, error                        |    |

|     | calculation, and weight update stages are performed in the accelerator                        |    |

|     | tiles whereas the weight gradient calculation is executed in the weight                       |    |

|     | gradient block. Tiles are connected via NoC. (R: NoC Router)                                  | 42 |

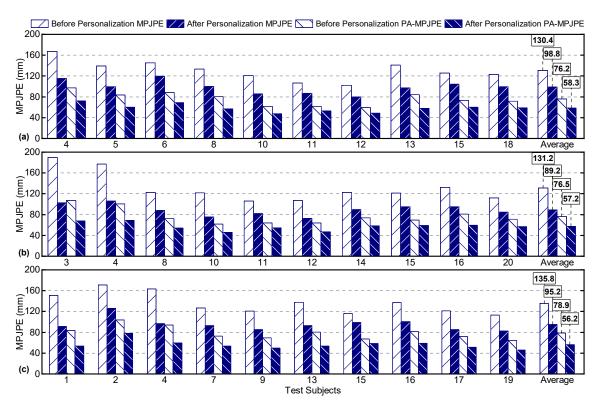

| 4.3 | MPJPE and PA-MPJPE comparisons for all three random sets. Results                             |    |

|     | show MPJPE and PA MPJPE before customization using 10 subjects                                |    |

|     | for training and after customization which is customized for each test                        |    |

|     | subject separately. Parts (a), (b), and (c) represent Set-1, Set-2, and Set-3                 |    |

|     | results, respectively. As they are randomly split, each plot shows the                        |    |

|     | results for different subjects                                                                | 46 |

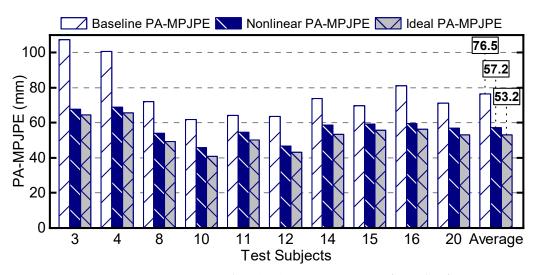

| 4.4 | PA-MPJPE comparisons for the baseline model (Baseline), a customized                          |    |

|     | model with nonlinear properties (Nonlinear), and a customized model                           |    |

|     | without nonlinear properties ( <i>Ideal</i> ) for 10 test subjects from <i>Set-2</i>          | 50 |

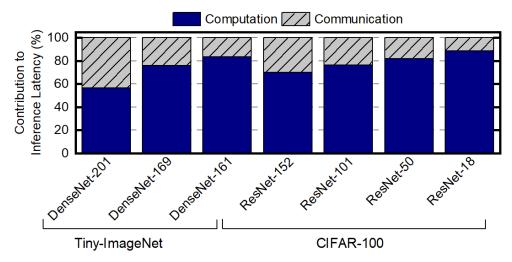

| 5.1 | Percentage contribution to inference latency for various networks on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|     | two datasets. The communication latency can take up to 43% of the total                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

|     | inference latency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53       |

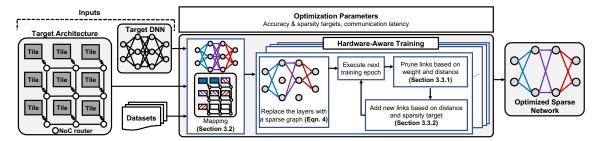

| 5.2 | Overview of the proposed approach. It consists of mapping the target DNN onto the target architecture using latency-aware mapping and hardware-aware dynamic sparse training. The training process first replaces the DNN layers with sparse graphs; then, at the end of each epoch, employs hardware-aware pruning and link addition. Each circle in the target DNN represents the feature map of DNNs; each link in the target DNN represents the weights of DNNs. The weights are mapped onto the in-memory computing (IMC) tiles with the same color as the corresponding links. The circles and the rectangles in the target |          |

|     | architecture denote the NoC routers and IMC tiles, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54       |

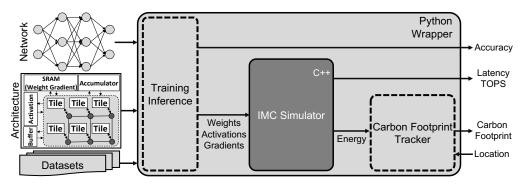

| 6.1 | Overview of the proposed framework. Inputs to the framework are the target network, target architecture, dataset, and location. First, the training or inference part is performed in the Python wrapper using the PyTorch library. This wrapper outputs the accuracy based on the quantization. Then, quantized weights, activations, and gradients are sent to the IMC simulator. This simulator outputs latency and TOPS. Then, energy consumption and location information are used by the                                                                                                                                    |          |

|     | carbon footprint tracker for each epoch, outputting the carbon footprint.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 58       |

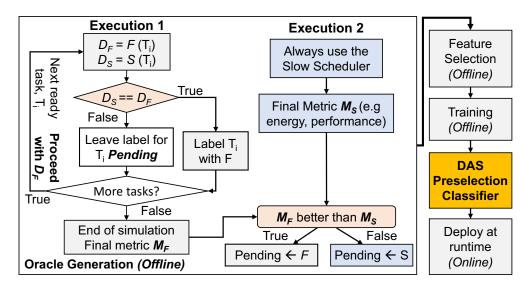

| 7.1 | Flowchart describing the flow of the DAS framework: Oracle generation,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>.</b> |

|     | feature selection, and training a model for the classifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 62       |

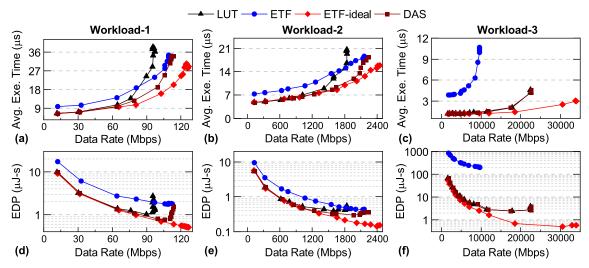

| 7.2 | Comparison of (a)–(c) average execution time and (d)–(f) EDP between                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| 7.0 | DAS, LUT, ETF, and ETF-ideal for three different workloads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 66       |

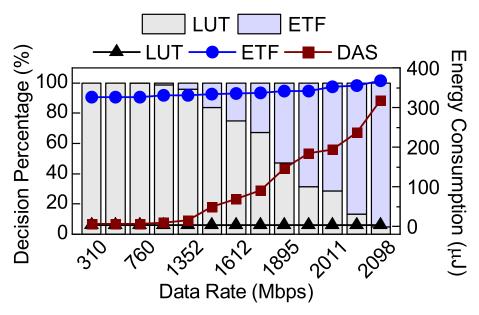

| 7.3 | Decisions taken by the DAS framework as bar plots and total scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|     | energy overheads of LUT, ETF, and DAS as line plots                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67       |

#### **ABSTRACT**

In-memory computing (IMC) based architectures enable energy-efficient inference and training of machine learning (ML) algorithms. As DNN complexity increases, the need for larger architectures is inevitable. Monolithic IMC architectures face yield and fabrication cost challenges because of significant area overhead. Hence, 2.5D/3D architectures are proposed for large-scale DNN accelerators using small chips (chiplets). Therefore, there is a critical need for research on designing optimized architectures for chiplets. In addition, there is an increasing demand to implement neural networks on mobile edge devices for both on-chip training and inference following recent developments in Internet of Things (IoT). Nonetheless, due to the significant computational resources required for training, deploying neural networks on edge devices with limited resources poses a challenge. The energy efficiency of IMC accelerators enables system designers to consider this architecture for edge devices. Therefore, on-chip training and inference using IMC architectures can enable energy-efficient edge computing. We perform research in the following areas to address these problems: (i) Big Little Chiplets: We develop a heterogeneous big-little chiplet-based IMC architecture that utilizes big and little IMC-based chiplets coupled with an optimal NoP configuration, (ii) On-Chip Training: We develop a ReRAM-based in-memory computing accelerator for on-chip training and inference of millimeter Wave (mmWave) CNN and inference of RGB CNN models for personalized home-based rehabilitation systems.

#### 1 INTRODUCTION

State-of-the-art deep neural networks (DNNs) have become more complex with deeper, wider, and more branched structures to cater to demanding applications [4, 5]. The growing complexity reduces hardware inference performance due to increased memory accesses and computations [4]. To boost the performance and energy efficiency, in-memory computing (IMC)-based architectures embed the matrix-vector-multiplications within the memory arrays [3, 6, 7, 8, 9]. However, IMC architectures with stationary weights stored on the chip result in significant area overhead and fabrication cost [2, 3]. Hence, 2.5D/3D architectures are adopted to design large-scale DNN accelerators using an array of small chips (i.e. chiplets) connected by a network-on-package (NoP) [10, 11].

Prior studies have demonstrated chiplet-based architectures based on both IMC and conventional multiply-and-accumulate (MAC) engines for DNN acceleration [2, 12, 1, 10, 13, 11, 14, 15, 16, 17, 18, 19, 20]. However, existing schemes do not consider the non-uniform distribution of weights and activations within DNNs while designing the chiplet-based architecture. Figure 1.1(a) and Figure 1.1(b) show the distribution of activations and weights (normalized) across all layers of ResNet-50 on ImageNet and VGG-19 on CIFAR-100. The initial layers have more activations between layers but have fewer weights. A larger number of activations lead to more on-chip data movement, while fewer weights imply reduced computations. In contrast, the latter layers have more weights and fewer activations, resulting in increased computations and reduced data movement. Hence, the chiplet-based IMC architectures should be optimized to match the non-uniform algorithm struc-

Figure 1.1: Normalized layer-wise activation/weight distribution for (a) ResNet-50 (ImageNet) and (b) VGG-19 (CIFAR-100). Initial/latter layers are activation/weight dominated.

ture and maximize the efficiency of computation and data movement across the DNN layers.

Figure 1.2(a) shows the IMC utilization of four different DNNs using a homogeneous chiplet-based RRAM IMC architecture. The architecture utilizes chiplets with 16 tiles, where each tile consists of an array of 16 IMC crossbar arrays of size  $256\times256$  [2]. The chiplets are interconnected by a 32-bit wide NoP operating at 250MHz, having the signaling scheme in [21]. Smaller DNNs like DenseNet-40 on CIFAR-10 have 29% IMC utilization, while larger DNNs like VGG-19 on CIFAR-100 achieve 40% IMC utilization. A lower IMC utilization leads to increased IMC array arrays and in turn, higher energy and latency. Furthermore, a single NoP structure

results in significant area overhead due to the large NoP driver and interconnect cost. Figure 1.2(b) shows that for the homogeneous structure, the NoP accounts for 90% and 50% of the total area for VGG-19 on CIFAR-100 and DenseNet-40 on CIFAR-10, respectively. In addition, the increased NoP bus width leads to higher NoP energy with up to  $53.75 \times$  higher cost relative to an 8-bit multiply-and-accumulate (MAC) operation in 16nm technology node [12].

Optimizing the architecture and the NoP will lead to efficient execution of DNN models. Therefore, this work addresses the inefficiency of homogeneous chiplet-based IMC architectures that fail to exploit the underlying distribution of weights and activations within DNNs. To this end, we propose a heterogeneous chiplet-based IMC architecture that integrates big and little-chiplet banks, as illustrated in Figure 2.1. Specifically, we develop an algorithm to determine the optimal configuration of the big-little IMC chiplet architecture. The little-chiplet bank consists of little chiplets interconnected by an interposer-based NoP (chiplets are placed closed to each other) [21]. Similarly, the big-chiplet bank consists of big chiplets interconnected by a bridge-based NoP [22]. Little chiplets consist of fewer/smaller IMC crossbars or processing element (PE) arrays, while the big chiplets have more/larger IMC crossbars or PE arrays. In addition, each chiplet (big/little) utilizes a local DRAM to store the weights of the DNN.

In addition to the hardware architecture, we also propose a new technique to map DNNs onto the big-little chiplet-based IMC architecture. Taking a cue from the non-uniform distribution of the weights and activations within the DNN, we propose to map the early layers within a DNN onto the little chiplet bank and the

Figure 1.2: IMC utilization for different DNNs using a homogeneous chiplet RRAM IMC architecture [2] and the proposed heterogeneous big-little chiplet architecture. The heterogeneous big-little architecture improves the IMC utilization.

subsequent layers onto the big chiplet bank. The smaller structure of the weights in the early layers results in higher utilization within the little chiplet bank, while the larger layers towards the end of the DNN achieve high utilization on the big-chiplet bank. To achieve this, we develop a custom mapping algorithm that performs the mapping of the DNN on to the big-little architecture. We note that, the algorithm is universal and applies to the case when the resource in a given big-little chiplet is not enough to store all DNN weights.

We exploit the activation distribution by utilizing an interposer-based NoP with high bandwidth within the little chiplet bank, which houses the early layers with higher on-chip data movement. Simultaneously, the subsequent layers with lower on-chip data movement (fewer activations) utilize the bridge-based NoP with lower bandwidth within the big chiplet bank. Experimental evaluation of

the proposed big-little chiplet-based RRAM IMC architecture on ResNet-50 on ImageNet shows up to  $259\times$ ,  $139\times$ , and  $48\times$  improvement in energy-efficiency with lower area compared to Nvidia V100 GPU, Nvidia T4 GPU, and SIMBA [1] architecture, respectively.

In addition, there is an increasing demand to implement neural networks on mobile edge devices for both on-chip training and inference following recent developments in the internet of things (IoT). Nonetheless, due to the significant computational resources required for training, deploying neural networks on edge devices with limited resources poses a challenge. One such case is home-based rehabilitation systems. Home-based rehabilitation using video cameras and wearable sensors has attracted significant attention due to its potential to help millions of people [23, 24, 25, 26]. For example, a recent study shows more than a two-fold increase in the number of amputations during the COVID-19 pandemic [27]. Remote monitoring and rehabilitation can complement infrequent and prolonged in-person visits to enable early diagnosis and intervention.

Prevalent use of home-based rehabilitation systems requires addressing three critical challenges. *First*, these systems must be sufficiently accurate to detect abnormal behavior and produce actionable data for health professionals. This requirement leads to the *second* challenge: sophisticated algorithms, such as machine learning (ML) and artificial intelligence (AI) techniques. Offloading these algorithms to the cloud is not a desirable solution since sending raw sensor data incurs high communication energy and latency while threatening user privacy. Hence, the *third* challenge is accomplishing home-based rehabilitation by running algorithms

locally, at the edge.

Recent techniques enable home-based rehabilitation using RGB cameras [23, 24], wearable inertial measurement units (IMU) [26], and millimeter-wave (mmWave) radar sensors [25]. These techniques collect sensor data as the patients perform rehabilitation movements. Then, they process the sensor data, typically using a convolutional neural network (CNN), to produce human joint coordinates. While these approaches show strong potential, they have one fundamental shortcoming. All prior techniques train their inference models with the user data available at design time. Then, they assume that future users, whose number is likely to be much larger than the training set, will use the produced model for inference. Even if the CNNs inference models generalize to arbitrary users, there is no guarantee that their accuracy will remain accurate. Hence, this limitation jeopardizes the first requirement: high accuracy in estimating the joint coordinates. As a result, there is a strong need for approaches that customize the deep learning models to specific users through on-device training in the home environment.

RGB cameras are the most common sources since they offer true-color real-world information. However, *always-on cameras at home* can raise serious privacy concerns such as facial information leakage. In contrast, mmWave radar, an emerging wireless sensing device, can accurately measure objects' moving trends while retaining privacy. In this work, we focus on systems that use mmWave radar inputs since they also have significantly lower processing requirements than RGB camera inputs and do not require users to wear any special sensors. We assume that an inference model, such as CNN, is trained offline to convert mmWave signals to human joint

positions. Then, it is acquired by a new patient for home-based rehabilitation. Since the accuracy of this model is limited by the offline data, the proposed system aims to customize the initial model to the new user, as illustrated in Fig. 4.1. The camera is activated only during this customization process to produce the human joint coordinates using the video frames. Then, these joint positions are used as a reference to supervise the incremental training of the inference model that uses the mmWave signals. After the customization, only the mmWave signals and corresponding inference model are used during the device lifetime, achieving over 13-fold inference time and 131-fold power consumption savings.

Current processors used for inference at the edge (e.g., at home) have limited processing capability due to their cost and energy constraint. For example, the Nvidia Jetson Xavier NX board can perform inference using mmWave inputs in 149.7 µs per input frame. However, training using RGB camera input reference takes 620 ms per frame on the same device. It can barely achieve a 1.6 frame per second (FPS) operation, which is impractical considering realistic 30 FPS or higher video frame rates. Storing the video frames and performing inference later is also not practical due to excessive memory requirements. Hence, practical solutions require novel AI hardware and methodologies to perform on-device training at the edge. To address this need, we propose an energy-efficient on-device training approach that enables personalized home-based rehabilitation, PHR. The proposed approach first generates the ground truth 3D joint coordinates data using RGB cameras. These coordinates are used to supervise on-device training. Then, we customize a baseline mmWave human pose estimation model using energy-efficient

on-device training. After the customization, our framework uses mmWave radar signals and the customized home-based rehabilitation model.

In summary, this preliminary report makes the following contributions:

#### **Big-Little Chiplets [28]:**

- We propose a heterogeneous big-little chiplet-based IMC architecture that utilizes a big and little IMC-based chiplet compute structure coupled with an optimal NoP configuration (interposer and bridge).

- We present a custom mapping strategy of DNNs onto the big-little chiplet IMC architecture that exploits the non-uniform distribution of weights and activations,

- Our experiments of the proposed big-little chiplet-based RRAM IMC architecture on ResNet-50 on ImageNet achieve up to 259×, 139×, and 48× improvement in energy-efficiency and lower area compared to Nvidia V100 GPU, Nvidia T4 GPU, and SIMBA [1] architecture, respectively.

### On-Chip Training [29]:

- An energy-efficient on-chip training framework that customizes mmWavebased human pose estimation model for higher accuracy.

- A Resistive RAM-based in-memory computing accelerator for on-chip training and inference of mmWave and inference of RGB models.

• Experimental results that demonstrate the practical real-life use of our framework, with a 28.01% lower error,  $611.1 \times$  lower inference energy, and  $14.0 \times$  faster training than a baseline model on Nvidia Jetson Xavier NX [30].

The rest of the report is organized as follows. The literature survey is discussed in Chapter 2. Chapter 3 presents the first completed preliminary work, Big-Little Chiplets for IMC of DNNs, and discusses its role in large-scale computing. The second completed preliminary work, energy-efficient on-chip training approach for personalized home-based rehabilitation systems is presented in Chapter 4. The first proposed work on sparse neural network optimization is discussed in Chapter 5. Chapter 6 presents the second proposed work on carbon footprint optimization. Other work that I have completed during my research is discussed in Chapter 7. Finally, Chapter 8 concludes this report.

## 2.1 Chiplet-based Architectures

Chiplet-based architectures are well explored for high-performance computing applications [14, 15, 10, 31, 16, 13, 32]. A co-design flow considering architecture, chip, and package for a chiplet-based system is proposed in [14]. A detailed design space exploration with the proposed co-design flow shows significant improvement in power consumption and area with respect to a monolithic design. Vivet et al. [15] proposed a chiplet-based system with 96 computing cores and a 3D memory are distributed over 6 chiplets. Another recent work proposed a 2,048 chiplet (14,336 cores) wafer-scale processor that utilizes a bridge-based integration [10]. The authors discuss the challenges of designing a wafer-scale processor and provide insights into power delivery, clock routing, and testing.

Chiplet-based architectures have proven to be both more energy-efficient and cost-effective than monolithic architectures for complex DNNs. Several prior studies proposed chiplet-based architectures for DNN acceleration [1, 33, 12]. The authors of [1] proposed a fine-grained 36-chiplet architecture for DNN inference acceleration. Each chiplet utilizes a homogeneous structure with 16 PEs that operate using a weight stationary dataflow. The chiplets are connected by a  $6\times6$  NoP mesh that utilize the ground-referenced signaling technique [21]. The authors of [12] proposed a hierarchical and analytical framework, NN-Baton, to analyze DNN mapping and communication overheads in a chiplet-based DNN accelerator. NN-Baton supports different mapping schemes of DNNs onto the chiplets. Furthermore, an

Figure 2.1: Cross-sectional view of the big-little chiplet-based IMC architecture. The architecture consists of a little chiplet bank with little chiplets (connected by an NoP within the interposer and a big chiplet bank with big chiplets connected by a bridge NoP. NoP properties: 1.5–8mm length, 2–4.5µm pitch, and 0.5–2µm width.

analytical model to quantify the communication overhead for NoP is also presented in NN-Baton. A family of chiplet topologies are proposed in [33]. The authors explored different chiplet topologies and compared their performance through an analytical metric which estimates latency. A chiplet-based IMC benchmarking tool for design space exploration, SIAM, is proposed in [2]. SIAM supports different chiplet architectures, IMC crossbar tile structures, NoP, NoC, and DRAM estimation. However, all prior studies assume a homogeneous chiplet structure across all chiplets interconnected by a single NoP. Furthermore, none of the prior works considered the non-uniform distribution of weights and activations in the DNN during the mapping process. Hence, many chiplets remain under-utilized while the large NoP leads to an increased area and energy overhead.

In contrast to prior works, we propose a heterogeneous big-little chiplet-based IMC architecture that combines big chiplet bank with a bridge-based NoP and a little IMC chiplet bank with an interposer-based NoP to enhance the IMC utilization and improve energy efficiency. Furthermore, we propose a customized methodology

that exploits the non-uniform distribution of DNN weights and activations in mapping the DNNs onto the big-little chiplet IMC architecture. To the best of our knowledge, this is the first heterogeneous chiplet-based IMC architecture that leverages different IMC structures collectively with a heterogeneous NoP coupled with a customized DNN mapping.

## 2.2 Home-based Rehabilitation Systems

Home-based rehabilitation systems draw significant attention, especially during the pandemic era, since they facilitate patient access to rehabilitation exercises at home and reduce in-person physical therapy sessions. To this end, researchers established the relationship between human joint location and rehabilitation movements [23, 24]. Authors in [23] proposed an approach that can get human joint information and face videos to relate the pain to the patient's movement. UI-PRMD [24] dataset provides exercise data using Kinect and motion capture system. To check whether the exercises conform to standards, rehabilitation systems require accurate human pose estimation, usually obtained from RGB images [34, 35]. OpenPose [34] and HRNet [35] are the most representative approaches that achieve fast and accurate human pose estimation from RGB sources.

mmWave radar-based pose estimation addresses privacy concerns and enhances robustness to the environment compared to RGB-based approaches, thus being an emerging solution for rehabilitation systems [25, 36, 37]. These approaches map 3D mmWave point cloud to ground truth human joints using smaller CNNs

than those processing RGB video ones since the mmWave frames are significantly smaller than their RGB counterparts. However, existing techniques focus on offline learning and algorithm design. Since they assume that offline-design CNNs will generalize to arbitrary users, they only consider inference during rehabilitation exercises. Hence, they do not deal with on-device training after a new patient starts using the system. In strong contrast, our proposed framework achieves end-to-end real-time mmWave-based human pose estimation, including training and inference.

The acceleration of both training and inference is critical for the real-time execution of applications. To this end, we utilize a Resistive RAM (ReRAM)-based in-memory computing (IMC) AI accelerator for our framework. IMC-based hardware accelerators perform computation inside memory units to reduce off-chip data communication. ReRAM-based approaches achieve high density and low energy consumption. Therefore, they are widely used for machine learning acceleration [3, 1, 38, 6, 28]. The training of CNN models is vulnerable to gradient precision and the write endurance and nonlinear properties of ReRAM architectures can cause an accuracy loss during training [39, 40]. Authors in [40] and [41] proposed methods to mitigate these problems. By utilizing these methods, on-chip training on ReRAM-based IMC accelerators is possible without seeing a significant accuracy drop.

In contrast to prior work, we propose PHR, a ReRAM-based IMC accelerator with energy-efficient on-chip training capacity for home-based rehabilitation systems. To the best of our knowledge, it is the first system that enables real-time processing of RGB image data, fast on-chip training of mmWave radar-based human pose

estimation, and energy-efficient model inference for continuous patient usage.

## 2.3 Task Scheduling Techniques for Heterogeneous Architectures

Schedulers have evolved significantly to adapt to different requirements and optimization objectives. Static [42, 43] and dynamic [44] task scheduling algorithms have been proposed in the literature. Completely Fair Scheduler (CFS) [44] is a dynamic approach that is widely used in Linux-based OS and aims to provide resource fairness to all processes while the static approaches presented in [42, 43] optimize the makespan of applications. CFS [44] was initially developed for homogeneous platforms, but it can also handle heterogeneous architectures (e.g., Arm big.LITTLE). While CFS may be effective for client and small-server systems, high-performance computing (HPC) and high-throughput computing (HTC) necessitate different scheduling policies. These policies, such as Slurm and HTCondor, are specifically designed to manage a large number of parallel jobs and meet high-throughput requirements [45, 46]. On the other hand, DSSoCs demand a novel suite of efficient schedulers that execute at nanosecond-scale overheads since they deal with scheduling tasks that can execute in the order of nanoseconds.

The scheduling overhead problem and scheduler complexities are discussed in [47, 48, 49]. The authors in [47] propose two dynamic schedulers, named as CATS and CPATH, where CATS detect the longest and CPATH detects the critical paths in the application. CPATH algorithm shows inefficiency in terms of its higher

scheduling overhead. Motivated by high scheduling overheads, [50] propose a new scheduler that approximates an expensive heuristic algorithm using imitation learning with low overhead. An imitation learning-based scheduler approximates an expensive heuristic with a low overhead [50]. However, the scheduling overhead is still approximately 1.1  $\mu$ s, making it inapplicable for DSSoCs with nanosecond-scale task execution. Energy-aware schedulers for heterogeneous SoCs have limited applicability to DSSoCs because of their complexity and large overheads [51, 52].

Several scheduling algorithms that demonstrate the benefits of using multiple schedulers are proposed in [53, 54, 55]. Specifically, the authors in [53] propose a technique that switches between three schedulers dynamically to adapt to varying job characteristics. However, the overheads of switching between policies are not considered as part of the scheduling overhead. The approach in [55] integrates static and dynamic schedulers to exploit both design-time and runtime characteristics for homogeneous processors. The hybrid scheduler in [55] uses a heuristic list-based schedule as a starting point and then improves it using genetic algorithms. However, it does not consider the scheduling overhead of the individual schedulers. The authors in [48] discuss the performance comparison of a simple round-robin scheduler and a complex earliest deadline first (EDF) scheduler and their applicability under different system load scenarios.

Using insights from literature, we propose a novel scheduler that combines the benefits of the low scheduling overhead of a simple scheduler and the decision quality of a sophisticated scheduler (described in Section 7.1.3) based on the system workload intensity. To the best of our knowledge, this is the first approach that uses

a novel runtime preselection classifier to choose between simple and sophisticated schedulers at runtime to enable scheduling with low energy and nanosecond scale overheads in DSSoCs.

#### 3 BIG-LITTLE CHIPLETS FOR IN-MEMORY ACCELERATION OF

#### DNNS: A SCALABLE HETEROGENEOUS ARCHITECTURE

### 3.1 Overall Architecture

Figure 3.1(a) shows the top-level block diagram of the heterogeneous big-little chiplet IMC architecture. The architecture consists of two banks of IMC chiplets, a little bank (shown in yellow color) and a big bank (shown in light red color). The little IMC chiplet bank consists of chiplets with smaller and fewer IMC crossbar arrays compared to the big chiplets. It is placed on an interposer that houses the NoP. The NoP provides high bandwidth and a compact structure for on-package communication within the little chiplet bank. At the same time, the increased size and count within the big chiplet bank allow for higher computation capability. The big chiplets are directly connected to the substrate using micro-bumps. A bridge-based NoP is utilized within the big chiplet bank for on-package communication. Long wires of the bridge NoP allow easy integration of the big chiplets. We utilize the Y–X routing methodology for the NoP. Each chiplet (big and little) consists of a local DRAM (DDR4 in this work) that stores the weights required for the IMC crossbar arrays.

Figure 3.1(b) shows the structure of a IMC chiplet. Each chiplet utilizes a hierarchical structure that consists of an array of big (bottom of Figure 3.1(c)) or little IMC tiles (top of Figure 3.1(c)) and each tile consists of an array of IMC crossbars or PEs. In addition, the chiplet contains a pooling unit, non-linear activation unit,

Figure 3.1: (a) Overview of the big-little chiplet IMC architecture. The little chiplet bank utilizes smaller chiplets connected by a interposer-based NoP while the big chiplet bank utilizes bigger chiplets connected by a bridge-based NoP. Each chiplet utilizes a local DRAM, (b) IMC chiplet architecture (big and little). Each chiplet consists of an array of IMC tiles and a dedicated NoP transceiver and router, (c) The little chiplet bank consists of fewer and smaller tiles while the big chiplet bank consists of more bigger tiles. Both chiplet structures utilize a mesh-based NoC for on-chip communication, and (d) Structure of each tile within the big and little chiplet. It consists of an array of IMC crossbar arrays and associated peripheral circuits with an interconnect similar to that in [3]. The little chiplet consists of fewer and smaller IMC crossbars while the big chiplet has larger and more IMC crossbar arrays.

accumulator, and buffer. The accumulator is used for the partial sum accumulation across different tiles within the chiplet. Furthermore, the buffers allow for efficient data movement in and out of the chiplet. Each IMC chiplet consists of a dedicated NoP transceiver used for the transmission and reception of packets across the NoP. In this work, we adopt the NoP transceiver from [21]. Each transceiver consists of a local PLL circuit that provides the clock for the transceiver. A five-port router is utilized for routing of the data across the NoP.

Each IMC chiplet utilizes a local DRAM to store the weights. The local DRAM allows for external memory access, thus making our proposed big-little architecture a generic platform. If a DNN does not fit on the entire chip, the DRAM stores all the

weights necessary for each chiplet. First, the DRAM loads the necessary weights into the IMC crossbar arrays. Next, while the computation is performed, the DRAM loads the next set of weights of the DNN. The buffer is designed to support a pingpong operation [56]. The weights from the DRAM are loaded into the first buffer stage (ping) and then moved to the second buffer stage (pong). Therefore, the big-little IMC chiplet architecture masks the DRAM latency with the computation latency, achieving high throughput.

Finally, Figure 3.1(d) shows the structure of an IMC tile. Each array in the crossbar consists of PEs that perform the computations. In this work, we focus on a resistive random-access-memory (RRAM) based IMC crossbar array due to its superior energy-efficiency [3]. The computations are performed in the analog domain by turning on all wordlines (WL) together and performing accumulation along the bitline (BL). The inputs are given through the WL while the weights are stored within the RRAM cells. Each IMC array consists of specialized peripheral circuitry that assists the computation. The peripheral circuitry includes a column multiplexer (mux), an analog-to-digital converter (ADC), a shift and add circuit, and a buffer. The column mux is used to share the ADC across columns of the IMC array. The ADC converts the MAC output in the analog domain across each column into the digital domain. The big-little IMC architecture does not utilize a digital-to-analog converter (DAC) by employing bit-serial computing. The shift and add circuit handles the positional value of each bit within the multi-bit input activations that are computed using the IMC arrays. The buffers within the tile are utilized for storing the partial sums and the input activations.

The following two sections present the implementation details and experimental evaluations, respectively.

# 3.2 Parameters of the Big-Little Architecture and Mapping

This section describes the implementation and mapping details of the Big-Little chiplet architecture.

The underlying non-uniform distribution of weights and activations within a DNN results in an increased number of activations in the early layers and larger number of weights in the subsequent layers (Figure 1.1). This non-uniform weight distribution leads to under-utilization of chiplets in the early layers, thus a lower overall IMC utilization. To improve the IMC utilization, crossbar arrays with smaller size (e.g. 32×32 instead of 128×128) can be used everywhere. However, using smaller crossbar arrays also leads to increasing number of chiplets in the system. In turn, larger number of chiplets in the system increases the area as well as energy consumption (due to higher relative area and energy of the peripheral circuits) masking the benefit of using chiplet-based system. Therefore, a balance between crossbar array size and number of chiplets in the system is necessary. To this end, we propose a technique to optimize the big-little chiplet configuration as discussed next.

### 3.2.1 Configuration of the big-little chiplets

We first determine the configuration of big-little chiplets by computing the tile utilization with different big-little chiplet configurations for a given DNN. Algorithm 1 shows our proposed technique to find the utilization. The inputs to the algorithm are

- 1. the set of crossbar sizes for the little chiplets  $(\mathfrak{X}_{\mathcal{L}})$  and the big chiplets  $(\mathfrak{X}_{\mathcal{B}})$ ,

- 2. set of number of tiles in the little chiplets  $(\mathcal{T}_{\mathcal{L}})$  and the big chiplets  $(\mathcal{T}_{\mathcal{B}})$ ,

- 3. number of little chiplets  $(N_{\mathcal{L}})$  and big chiplets  $(N_{\mathcal{B}})$ ,

- 4. the DNN structure,

- 5. the total number of chiplets in the system.

We note that the initial layers of the DNN are mapped on to little chiplets since there are fewer weights in the initial layers. A DNN layer is mapped on to a chiplet when number of tiles required for that layer is less than the number of remaining tiles in the chiplet, i.e., the available resource on the chiplet is sufficient for the layer (as shown in line 13–17 of Algorithm 1). Once a layer (layer-j) is mapped on to a chiplet, the tile utilization is computed as:

$$IMC_{j} = \left\lceil \frac{K_{j}^{x} \times k_{j}^{y} \times N_{j}^{if}}{x} \right\rceil \times \left\lceil \frac{N_{j}^{of} \times Q}{x} \right\rceil$$

$$u_{j} = 100 \times \frac{K_{j}^{x} \times k_{j}^{y} \times N_{j}^{if} \times N_{j}^{of} \times Q}{IMC_{i} \times x \times x}$$

(3.1)

where  $K_j^x$  and  $K_j^y$  are the kernel sizes of layer-j,  $N_j^{if}$  and  $N_j^{of}$  are the number of i/p and o/p features for layer-j, Q is the quantization precision, IMC<sub>j</sub> is the number of IMC crossbars required for layer-j and x is the IMC crossbar size  $(x \times x)$ . Once the resources of a chiplet are exhausted, the next chiplet is considered for mapping. This process continues until no chiplet (little/big) is available.

In the proposed method, for each chiplet configuration, we obtain the average utilization for a particular DNN after each layer is mapped (line 36 of Algorithm 1). Then we sort (in descending order) the configurations based on the utilization and save the top K configurations. The above procedure is repeated for M different DNNs and the configuration with highest utilization which is common for all DNNs is considered as the final configuration for the big-little chiplet system. We note that K and M are user-defined parameters and our proposed technique is independent of these parameters.

## 3.2.2 Configuration of the big-little NoP

The heterogeneous chiplet configuration (discussed in Section 3.2.1) improves the overall chiplet utilization by using smaller chiplets that match well to the early layers with fewer weights. However, the initial DNN layers produce higher number of activations compared to later layers. Therefore, the volume of traffic between little chiplets (used for initial DNN layers) is higher than the traffic volume between big chiplets (used for later DNN layers). Hence, the network-on-package (NoP) configuration between little chiplets needs to be different than that of the big chiplets. To this end, we propose a technique to determine optimal NoP configuration for a

system with big-little chiplet targeted for a particular DNN. Algorithm 2 shows the technique to determine NoP configuration for a particular DNN. The inputs to the algorithm are:

- 1. big-little chiplet configuration obtained from Algorithm 1,

- 2. set of NoP bus width for the little chiplets  $(W_{\mathcal{L}})$  and the big chiplets  $(W_{\mathcal{B}})$ ,

- 3. set of NoP frequency for the little chiplets  $(\mathcal{F}_{\mathcal{L}})$  and the big chiplets  $(\mathcal{F}_{\mathcal{B}})$ ,

- 4. the DNN structure.

We evaluate the energy-delay product of communication for each NoP configuration in the set of configurations. An analytical expression based evaluation is incorporated to perform fast exploration in the NoP configuration space. First, we evaluate communication volume of each NoP configuration given a particular DNN. The communication volume is equivalent to the number of packets transferred between two chiplets, and the number of packets (P) is expressed as  $P = \frac{b}{w}$ , where b is the number of bits to be communicated and w is the NoP bus width. We divide the number of packets by NoP frequency (f) to obtain an approximation of NoP latency  $d = \frac{P}{f} = \frac{b}{w \times f}$ . Next, we compute NoP power consumption by assuming that it is proportional to cube of NoP frequency [57];  $p = f^3$ . Then the approximate energy consumption (e) is computed by multiplying communication latency and communication power;  $e = d \times p$ . Finally, communication EDP between each pair of chiplet (edp) is computed as:

$$edp = e \times d = d \times p \times d = d^2 \times f^3 = \left(\frac{b}{w \times f}\right)^2 \times f^3 = \frac{b^2 \times f}{w^2}$$

(3.2)

The total communication EDP for each NoP configuration for a particular DNN is obtained by adding the communication EDP between each pair of chiplets. A total of K NoP configurations with lower EDP are saved and the above procedure is repeated for M different DNNs. The configuration with lowest cost which is common for all DNNs is considered as the final NoP configuration for the big-little chiplet system. Similar to the technique of selecting big-little chiplet configuration (described in Section 3.2.1), K and M are the user defined parameter and our proposed technique is independent of these parameters.

## 3.2.3 Mapping a Previously Unseen DNN to a System on big-little Chiplets

So far, we described our proposed technique to determine the optimal configuration of big-little chiplet and the NoP. The optimal configuration is determined by performing design space exploration with several DNNs. However, an unknown DNN (not seen before) may be encountered at runtime. Moreover, there is no guarantee that all the weights of a given DNN will fit in the on-chiplet resources since the number of DNN parameters seem to be continuously growing. In these cases, we need to divide the entire DNN into multiple parts and load the weights of each part from DRAM before executing. Algorithm 3 shows the DNN partitioning as well as the mapping technique. The input to the algorithm is the DNN structure, big-little chiplet configuration and big-little NoP configuration. First, we compute the number of in-memory computing bits available on the system (S<sub>B</sub>). Specifically, for each type (little/big) of chiplets, we multiply the number of available chiplets

$(n_l/n_b)$ , the number of tiles in each chiplet  $(t_l/t_b)$ , the number of crossbar array in each tile (16), and the size of IMC crossbar array for big and little chiplets  $(x_l/x_b)$ . Then we add the product for big and little chiplets to obtain the total number of in-memory computing bits available on the system  $(S_B)$ :

$$S_{B} = (n_{l} \times t_{l} \times 16 \times x_{l} \times x_{l}) + (n_{b} \times t_{b} \times 16 \times x_{b} \times x_{b})$$

$$(3.3)$$

Next, we compute the number of bits required to store all the weights of the DNN  $(D_B)$ . Assuming average utilization of  $\mathfrak{u}(0<\mathfrak{u}\leqslant 1)$ , the total number of partitions (Pr) required for the DNN is computed by taking the ceiling of the quotient obtained by dividing the required number of bits to store all weights  $(D_B)$  by the available number of in-memory bits on the system  $(S_B)$ :

$$Pr = \left\lceil \frac{D_B}{S_B \times u} \right\rceil \tag{3.4}$$

For each partition, first, we compute the utilization of  $\mathfrak{i}^{th}$  layer on a big chiplet  $(U_B^i)$  as well as on a little chiplet  $(U_L^i)$ . We compute  $U_B^i$  and  $U_L^i$  using Equation 3.1. If the big chiplet utilization  $((U_B^i))$  is less than the little chiplet utilization  $(U_L^i)$  and the little chiplet bank is not exhausted, then the layer is mapped onto a little chiplet, as shown in lines 7–12 of Algorithm 3. Otherwise, we compute the number of big chiplets required  $(\mathfrak{a}_B)$  to map the rest of the layers. If  $\mathfrak{a}_B$  is less than or equal to the number of available big chiplets  $(A_B)$ , then we map the rest of the layers to the big chiplet bank, else the algorithm throws an error since the resource requirement exceeds the available capacity (shown in line 18–23 of Algorithm 3). Thus, we

ensure that the initial layers with fewer weights are mapped into little chiplets and the latter layers with higher number of weights are mapped onto big chiplets with more computation resources. Therefore, our proposed custom mapping of the DNN onto the big-little chiplet architecture ensures high IMC utilization.

## 3.3 Experimental Evaluation

## 3.3.1 Experimental Setup

Evaluation platform: To evaluate the proposed heterogeneous big-little IMC chiplet architecture, we use a customized version of the open-sourced tool SIAM [2]. The customization includes the addition of the custom mapping scheme detailed in Section ??. In addition, we handle the big-little chiplet IMC architecture by adding the number of each type (big/little) of chiplets, the number of tiles inside big and little chiplets, and the big-little IMC structure. Furthermore, we also assume that each type of chiplet can use different NoP width. The simulator performs the mapping of a given DNN onto the big-little IMC chiplet architecture. The outputs include area, energy, latency, throughput, energy efficiency, and IMC utilization (for all individual components in the architecture). Finally, we add support for intermediate DRAM access (DDR4 [58]) for each chiplet to handle the case where all weights do not fit on the system at once. We plan to open-source the tool and optimization methodology upon acceptance of the paper.

**DNN algorithms and architectural parameters:** We evaluate the proposed heterogeneous chiplet architecture with DenseNet-40 (0.26M) on CIFAR-10, ResNet-

Table 3.1: Set of configurations considered to determine big-little chiplet and NoP structure.

| Chiplet              | Configuration     | 1                             | NoP Configuration           |

|----------------------|-------------------|-------------------------------|-----------------------------|

| Parameter            | Values in the Set | Parameter                     | Values in the Set           |

| $\chi_{\mathcal{L}}$ | {32, 64}          | $ \mathcal{W}_{\mathcal{L}} $ | {16, 32, 64}                |

| $\chi_{\mathcal{B}}$ | {128, 256, 512}   | $W_{\mathcal{B}}$             | {4, 8, 12, 16, 20, 24}      |

| $	au_{\mathcal{L}}$  | {9, 16, 25}       | $\mathcal{F}_{\mathcal{L}}$   | {600, 1000, 1400, 1800} MHz |

| $	au_{\mathcal{B}}$  | {36, 49}          | $\mathcal{F}_{\mathcal{B}}$   | {600, 800, 1000} MHz        |

110 (1.7M) on CIFAR-10, VGG-19 (45.6M) on CIFAR-100, ResNet-34 (21.5M) and ResNet-50 (23M) on ImageNet. We utilize an RRAM-based IMC structure for DNN inference with the following parameters: one bit per RRAM cell, a  $R_{\rm off}/R_{\rm on}$  ratio of 100, ADC resolution of 4-bits with 8 columns multiplexed, operating frequency of 1GHz [59, 3], and a parallel read-out method. We use 8-bit quantization for the weights and activations, and a 32nm CMOS technology node. The chiplets are placed to achieve the least Manhattan distance. The NoP parameters include  $E_{\rm bit}$  of 0.54pJ/bit [21], interconnect parameters width, length, and pitch for the interposer-based NoP from [21] and for bridge-based NoP from [60] (Figure 2.1), per lane NoP TX/RX area of 5,304  $\mu$ m², and NoP clocking circuit area of 10,609  $\mu$ m² [61]. In addition, we also model the  $\mu$ bump for both the interposer [62] and bridge-based [63] NoP by utilizing the PTM models [64].

Table 3.2: Performance comparison of each component of a homogeneous (Little only, Big only) chiplet architecture and the heterogeneous Big-Little IMC chiplet architecture for VGG-19 on CIFAR-100.

| Configuration         | T           | Area                     |                       |      |      | E    | nergy |                       |      |     | Lat | tency |                       |

|-----------------------|-------------|--------------------------|-----------------------|------|------|------|-------|-----------------------|------|-----|-----|-------|-----------------------|

| 000                   | IMC   NoP   |                          | Normalized to         | IMC  | NoP  |      |       |                       |      |     |     |       | Normalized to         |

|                       | (%) (%)     | (%)   (mm <sup>2</sup> ) | big-little $(\times)$ | (%)  | (%)  | (%)  | (mJ)  | big-little $(\times)$ | (%)  | (%) | (%) | (ms)  | big-little $(\times)$ |

| Little only           | 11.9   88.0 | 0.1   952.1              | 10.9                  | 99.7 | 0.2  | 0.1  | 1.3   | 4.1                   | 99.7 | 0.1 | 0.2 | 1.6   | 1.3                   |

| Big only              | 44.0   55.5 | 0.5   597.2              | 6.8                   | 78.6 | 11.0 | 10.4 | 0.43  | 1.3                   | 99.6 | 0.1 | 0.3 | 3.2   | 2.7                   |

| Big-Little (this work | 52.4   47.4 | 0.2   87.4               | 1.0                   | 99.8 | 0.1  | 0.1  | 0.32  | 1.0                   | 99.2 | 0.3 | 0.5 | 1.2   | 1.0                   |

Figure 3.2: IMC utilizations for different DNNs across different big-little chiplet-based RRAM IMC configurations for (a) ResNet-110, (b) ResNet-34, (c) VGG-19, (d) DenseNet-40. Based on the utilization, we choose crossbar size of big chiplet as  $256 \times 256$  and crossbar size of little chiplet as  $64 \times 64$  (256–64).

## 3.3.2 Big-Little IMC Structure and NoP

This section demonstrates the parameters related to big-little IMC structure and big-little NoP. Specifically, we consider four DNNs (mentioned in Section 3.3.1) and execute Algorithm 1 to determine the top 10 (K=10) configurations with highest utilization for each DNN. We consider a system with 36 chiplets to limit the total area and power consumption of the system. Table 3.1 shows the input parameters  $(\mathcal{X}_{\mathcal{L}}, \mathcal{X}_{\mathcal{B}}, \mathcal{T}_{\mathcal{L}}, \mathcal{T}_{\mathcal{B}})$  to the algorithm. We vary the number of little chiplets from 1 to 35 while maintaining the total number of chiplets to be 36. Then, we choose the best configuration which is common for all four DNNs. We observe that a system with 25 little chiplets with a  $64 \times 64$  IMC crossbar and 25 tiles per chiplet, and 11 big chiplets

with a  $256 \times 256$  IMC crossbar and 36 tiles per chiplet provides best utilization across all four DNNs. Figure 3.2 shows the utilization for a system with 25 little and 11 big chiplets with varying size of crossbars (both for big and little chiplet) for all four DNNs. In this case, we also fixed the number of tiles per chiplet to 25 for the little chiplets and 36 for the big chiplets. Figure 3.2 reveals that the configuration where the crossbar size of the big chiplets is  $256 \times 256$  and the crossbar size of the little chiplets is  $64 \times 64$  (256-64, 256 denotes crossbar size of big chiplets and 64 denotes crossbar size of little chiplets) shows higher utilization than other configurations for three out of four DNNs. Only in the case of ResNet-110, the configuration 256-32 shows higher utilization than 256-64. However, we choose 256-64 over 256-32 since it provides more on-chip resources, lower area and energy efficiency for the IMC crossbar array (due to peripheral circuits).

Similarly, we execute Algorithm 2 for four DNNs to obtain the NoP configuration. Table 3.1 shows the set of different NoP parameters ( $W_{\mathcal{L}}$ ,  $W_{\mathcal{B}}$ ,  $\mathcal{F}_{\mathcal{L}}$ ,  $\mathcal{F}_{\mathcal{B}}$  used as inputs to Algorithm 2). The parameters are adopted from [65]. EDP for NoP is obtained for all NoP configurations for the four DNNs. Then, the NoP configuration having the lowest EDP for all four DNNs is chosen. Based on the EDP results, the big NoP frequency and the little NoP frequency is set to 600 MHz and 1 GHz, respectively; the big NoP bus width and the little NoP bus width is set to 24 and 32, respectively. Figure 3.3 shows the normalized NoP EDP for different combination of bus width for big and little chiplets. For illustration purpose, we show VGG-19 and ResNet-34 since these two DNNs utilize more than 34 out of 36 chiplets. From Figure 3.3, it is observed that the configuration with big NoP bus width of 24 and little NoP bus

Figure 3.3: Normalized NoP EDP for different bus-widths for VGG-19 and ResNet-34. The NoP with bus width of 24 for big and 32 for little chiplets (24–32) shows lowest EDP.

Table 3.3: Performance comparison of a homogeneous (Little only, Big only) chiplet architecture and the heterogeneous Big-Little IMC chiplet architecture for different DNNs.

| Configuration         |         | Utilization (%)     | Area (mm²)                        | Energy (mJ)                    | Latency (ms)                   |

|-----------------------|---------|---------------------|-----------------------------------|--------------------------------|--------------------------------|

| Comiguration          | Res-110 | VGG-19 Dense-40 Res | 34 Res-110 VGG-19 Dense-40 Res-34 | Res-110 VGG-19 Dense-40 Res-34 | Res-110 VGG-19 Dense-40 Res-34 |

| Little only           | 69      | 92   58   9         | 3   171.7   952.1   71.5   657.8  | 1.4   1.3   0.22   41.1        | 23.0   1.6   1.6   13.1        |

| Big only              | 44      | 59   32   8         | 2   220.0   597.2   220.2   595.9 | 0.28   0.43   0.11   3.7       | 1.1   3.2   0.02   20.2        |

| Big-Little (this work | s) 88   | 93   90   9         | 87.4   87.4   87.4   87.4         | 0.18   0.32   0.06   8.2       | 1.1   1.2   0.03   48.6        |

width of 32 shows the lowest EDP. Since little chiplets produce higher number of activations than the big chiplets, it is intuitive that little NoP are wider (larger bus width) than the big NoP.

# 3.3.3 Comparison with Baseline Architectures with Homogeneous Chiplets

We compare the performance of our proposed big-little chiplet architecture with respect to two baseline architectures with homogeneous chiplets [2]. 1) Little

**only:** In this configuration, we consider a system where the configuration of all chiplets as well as the NoP is same as that of the little chiplets. **2**) **Big only:** In this configuration, we consider a system where the configuration of all chiplets as well as the NoP is same as that of the big chiplets. We note that, the total number of chiplets with 'Little only' and 'Big only' configurations vary for different DNNs.

Table 3.2 shows the performance comparison for 'Little only', 'Big only' and the proposed big-little architectures for VGG-19 on CIFAR-100. In this table, the performance of each component of the architecture, i.e. IMC, NoP and NoC is shown. Our proposed big-little chiplet architecture results in a balanced distribution of the area among the circuit and NoP components, while the NoC accounts for a minimal portion (0.2%) of the total area. In 'Little-only' architecture, NoP becomes the bottleneck for area since the chiplets have smaller size, hence more number of chiplets are required which increases the NoP. In 'Big only' architecture, NoP consumes more energy due to higher volume of data movement between each pair of chiplets. In contrast, the proposed big-little architecture with its high IMC utilization and reduced on-chip communication as well as on-package data movement results in less total energy consumption and less inference latency. Overall, the proposed heterogeneous big-little architecture achieves up to  $10.9 \times$  lower area,  $4.1 \times$  lower energy, and  $2.7 \times$  lower latency than 'Little only' and 'Big only' architectures.

Next, we compare the IMC utilization and the performance (area, energy and latency) for ResNet-110, VGG-19, DenseNet-40, and ResNet-34 against 'little only' and 'big only' architecture. For VGG-19, our proposed big-little architecture achieves the highest IMC utilization of 93% compared to 92% and 59% for 'Little only' and

'Big only', respectively. Similarly, the big-little architecture achieves 88%, 90%, and 98% IMC utilization for ResNet-110, DenseNet-40, and ResNet-34, respectively, up to 2.8× greater than 'Little only' and 'Big only' architectures. We observe that the big-little architecture provides up to  $7.8 \times$  improvement in energy and up to  $21 \times$ improvement in inference latency with respect to baseline homogeneous architectures. 'Big only' architecture consumes less energy and less latency than big-little architecture for ResNet-34, but in this case, the area of 'Big only' is 6.8× higher than big-little architecture. To better analyze the performance comparison, we plot the energy-delay-area product (EDAP) for all DNNs, as shown in Figure 3.4. The big-little chiplet architecture provides up to 329× lower EDAP than the 'Little only' and 'Big only' architectures across all four DNNs. Although 'Big only' architecture shows improvement in energy consumption and inference latency with respect to big-little for ResNet-34, the EDAP with 'Big only' is 1.3× higher than big-little architecture in this case. Hence, the proposed big-little IMC architecture achieves optimal performance through reduced EDAP at higher IMC utilization across different DNNs.

# 3.3.4 Results with DRAM (DDR4)

In this section, we show the performance results when the resource on a big-little chiplet-based system is not sufficient to store all the weights of a given DNN. In that case, the DNN is divided into multiple partitions. One partition is mapped on to the big-little chiplets at a time. While the computations of a partition of the DNN are performed, the weights corresponding to the next partition are loaded

Figure 3.4: EDAP comparison (log-scale) of the big-little chiplet-based RRAM IMC architecture to 'Little only' and 'Big only' chiplet-based RRAM IMC architectures. The big-little architecture achieves up to  $329\times$  improvement compared to 'Little only' architecture.

from the DRAM into the ping-pong buffer. The additional DRAM accesses result in increased energy. At the same time, the impact on latency is reduced through the ping-pong buffers [56]. Table 3.4 shows the ratio between DRAM energy and compute energy for VGG-16 and VGG-19 with systems having different number of chiplets. We observe that, the ratio of DRAM energy to computation energy increases with reduction in the system sizes for both the DNNs. With decreasing system size, more weights need to be stored and loaded from DRAM, thereby increasing DRAM energy.

## 3.3.5 Comparison with State-of-the-art Work

Table 3.5 shows the comparison of the proposed heterogeneous big-little RRAM IMC chiplet architecture with an Nvidia T4 and V100 GPU, and SIMBA [1]. The

Table 3.4: Ratio between DRAM energy and compute energy for VGG-16 and VGG-19 with systems having different number of chiplets (\*\*All weights of VGG-19 fit on chip with this configuration, significantly reducing the DRAM energy).

| # Chiplets  | VGG-1       | .6    | VGG-19      |        |  |  |

|-------------|-------------|-------|-------------|--------|--|--|

| " Crap ross | #partitions | Ratio | #partitions | Ratio  |  |  |

| 36          | 2           | 1.1   | 1           | 0.08** |  |  |

| 25          | 2           | 2.1   | 2           | 131    |  |  |

| 16          | 3           | 3.6   | 2           | 161    |  |  |

Table 3.5: Comparison with other platforms for ResNet-50 on ImageNet (\*reported in [1]).

| Platform               | Area (mm²) | Energy Efficiency (Images/s/W) |

|------------------------|------------|--------------------------------|

| Nvidia V100 GPU*       | 815        | 8.3                            |

| Nvidia T4 GPU*         | 525        | 15.5                           |

| SIMBA [1]              | 215        | 45                             |

| Big-Little (this work) | 85         | 827                            |

big-little chiplet architecture achieves a lower area for the architecture due to the custom RRAM-based IMC and the optimized NoP structure. Compared to the Nvidia V100, Nvidia T4, and SIMBA architecture, the big-little IMC architecture achieves  $9.6\times$ ,  $6.2\times$ , and  $2.5\times$  area improvement and  $99.6\times$ ,  $53.4\times$ , and  $18.4\times$  energy-efficiency improvement, respectively. The improved energy efficiency is attributed to the higher IMC utilization, analog computation within the RRAM-based IMC, reduced NoP data movement and bus width, and the absence of intermediate DRAM transactions for weights and partial sums.

#### Algorithm 1 Determining Big-Little Chiplet Configuration

- 1: **Input:** DNN structure, number of chiplets (N<sub>C</sub>), set of crossbars sizes for the little chiplets  $(\mathfrak{X}_{\mathcal{L}})$  and the big chiplets  $(\mathfrak{X}_{\mathcal{B}})$ ; set of number of tiles in the little chiplets  $(\mathcal{T}_{\mathcal{L}})$  and the big chiplets  $(\mathcal{T}_{\mathcal{B}})$ ; number of little chiplets  $(\mathcal{N}_{\mathcal{L}})$  and number of big chiplets  $(N_B)$

- 2: **Output:** Tile utilization for each configuration  $i(U_i)$